據(jù)IT之家從臺(tái)積電官方獲悉,臺(tái)積電的 3nm 工藝家族包括四個(gè)版本,分別是基礎(chǔ)的 N3、成本優(yōu)化的 N3E、性能提升的 N3P 和高壓耐受的 N3X。其中,N3E 和 N3P 都是基于 N3 的光學(xué)縮小版,可以降低復(fù)雜度和成本,同時(shí)提高性能和晶體管密度。而 N3X 則是專為 HPC 領(lǐng)域設(shè)計(jì)的工藝,可以支持更高的電壓和頻率,從而實(shí)現(xiàn)更強(qiáng)的計(jì)算能力。

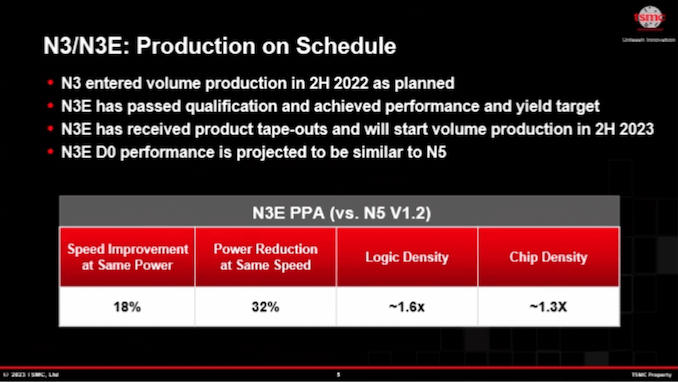

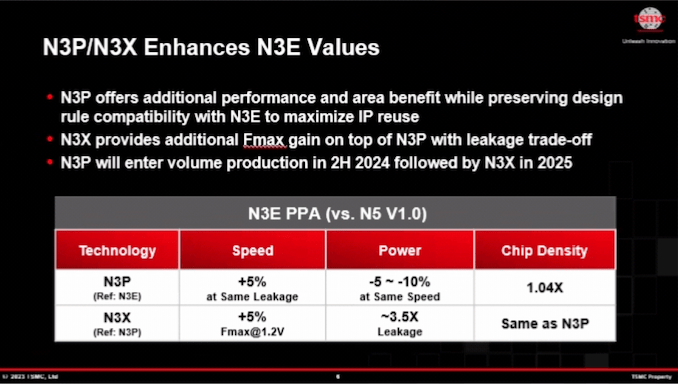

根據(jù)臺(tái)積電的數(shù)據(jù),與 5nm 工藝相比,N3E 可以在相同頻率下降低 32% 的功耗,或者在相同功耗下提高 18% 的性能。而相較于 N3E,N3P 則可以在相同功耗下提高 5% 的性能,或者在相同頻率下降低 5%~10% 的功耗。同時(shí),N3P 還可以將晶體管密度提高 4%,達(dá)到 1.7 倍于 5nm 工藝的水平。

而 N3X 則是臺(tái)積電 3nm 工藝家族中最強(qiáng)悍的版本,它可以在相同功耗下比 N3P 提高 5% 的性能,達(dá)到 1.2 伏特以上的電壓水平。這對(duì)于一個(gè) 3nm 級(jí)別的工藝來(lái)說(shuō)是非常極端的,也意味著會(huì)有很高的功耗和發(fā)熱問(wèn)題。因此,這個(gè)工藝只適合用于 HPC 級(jí)需要極致性能的處理器,并且需要芯片設(shè)計(jì)者采取有效的措施來(lái)控制溫度和功耗。

臺(tái)積電表示,N3E 將在 2023 年下半年開始量產(chǎn),而 N3P 和 N3X 則分別在 2024 年下半年和 2025 年投入量產(chǎn)。這些工藝都將采用 FinFET 結(jié)構(gòu),也就是金屬氧化物半導(dǎo)體場(chǎng)效應(yīng)晶體管(MOSFET)結(jié)構(gòu)。這種結(jié)構(gòu)已經(jīng)被臺(tái)積電使用了多年,并且有著成熟和穩(wěn)定的特點(diǎn)。

不過(guò),在 2nm 級(jí)別以下,臺(tái)積電將采用新型的 GAAFET 結(jié)構(gòu),也就是門全包圍場(chǎng)效應(yīng)晶體管(Gate-All-Around FET)結(jié)構(gòu)。這種結(jié)構(gòu)可以進(jìn)一步提高晶體管密度和性能,并且降低功耗和泄漏。臺(tái)積電稱,2 納米制程在良品率和元件效能進(jìn)展良好,將如期于 2025 年量產(chǎn)。臺(tái)積電介紹稱,相較于 N3E 制程技術(shù),2 納米在相同功耗下,速度最快將可增加 15%;在相同速度下,功耗最多可降低 30%,同時(shí)晶片密度增加逾 15%。